Siltronic AG - Unexpectedly High-Quality In A New Regime

Integral To The Semiconductor Industry

Over a decade ago the semiconductor wafer (a.k.a. substrate or slice) market was characterised by brutal cyclicality, where prices and volumes would fall significantly during downturns, threatening substrate manufacturers’ existence. Since then key factors have changed; capital allocation discipline, favourable developments in demand and customer economics, and the increasing technological sophistication required to produce virgin wafers have enabled the more concentrated industry to exercise pricing power consistently. While the fact that wafer manufacturers are almost at the end of the semiconductor industry’s supply chain bullwhip means that volumes are likely to be down significantly this year, long term agreement (LTA) usage and utilisation levels going into this downturn are higher than in previous cycles, supporting prices. Mid to long term the outlook for wafer manufacturers remains very positive, but even short term Siltronic’s shares are pricing in unrealistic scenarios.

Virgin wafer manufacturing is a highly technologically advanced process and only getting more complicated. Producing high quality substrates requires advanced material science knowledge and precision machining capabilities at nanometer levels, posing significant barriers to entry secured through scale and IP.

Physics is increasingly favouring higher chip areas over transistor density, boosting the outlook for wafer producers. Semiconductor manufacturers are increasingly struggling with physical and economic limitations on transistor density. Under this new regime industry players are using their newfound leverage to secure significant long-term agreements before expanding capacity.

The market is pricing in irrational scenarios and disregarding FabNext’s potential. At guided flat prices the market is expecting Siltronic’s volume to decline more than industry volumes did over the GFC (‘08&’09 combined). This not only disregards an expected strong recovery, but a conservatively estimated incremental EUR 100m in EBIT coming online over the next 4 years secured under LTAs.

Siltronic AG

Figure 1: 5 Year Average Market Share based on USD Revenue (Company Filings and SEMI)

Siltronic AG is a manufacturer of hyper pure silicon wafers which form the surface on which semiconductors are built. With a stable 14% market share, the Munich based company is one of the 5 dominant players (see Fig. 1), which combined provide more than 90% of world substrate supply. Founded in 1968 as a subsidiary of one of the seven sisters[1], Wacker Chemie AG, Siltronic provides high grade polished and epitaxial (epi) wafers for use in memory, logic, MEMS, image sensors and other semiconductor devices. The company spun out of Wacker when it IPO'd in 2015, at ca. 31%, its former parent remains the company's largest shareholder to date.

Around 65% of Siltronic's portfolio consists of 300mm double sided polished and epi wafers. The 300mm epis are mainly used in logic and analog chips, while the polished slices are primarily used in memory. Epitaxial wafers are wafers with an additional monocrystalline silicon layer added through chemical vapor deposition, which makes it possible to select material properties independently of the polished substrate, and consequently create wafers with properties that differ from those of the underlying slice. The remaining 35% of Siltronic's portfolio are smaller diameter wafers (200mm and below), which are also sold in polished, epi, and more specialized forms. The smaller substrates are mainly used in logic, analog, discrete and image sensors, but are also used for power controllers and optoelectronics.

Siltronic manufactures its products in the United States (Portland: 200mm), Germany (Freiberg: crystal pulling, 300mm, small diameter), and Singapore (crystal pulling, 200mm and 78% ownership of Samsung JV for 300mm). The company is also about to bring another Singaporean 300mm facility, FabNext, online in early 2024, which, over time, will significantly increase its capacity (ca. +1/3). Another important fact is that more than 65% of the Siltronic's sales are subject to long-term agreements, which usually have a term of 3-5 years and specify minimum volumes, prices, and required prepayments towards the contracted product.

Figure 2: Wafer Manufacturing Process (Siltronic AG)

Both in terms of size and use case, Siltronic's portfolio is quite similar to the market. However, the company's wafers tend to be used for higher value, more advanced lithography processes due to their high quality. A wafer's quality can be assessed along several dimensions, with nearly every step in the manufacturing process (see Fig. 2) having a significant impact on the end result. The monocrystalline silicon ingot created through czochralski pulling or the float zone method, for example, can be judged based on mechanical stability, homogeneity, oxygen content, resistivity, purity, doping level, etc. All of these characteristics are not only dependent on the quality of polysilicon used, but the temperature applied, pulling speed used, atmosphere the material is subjected to etc. The final wafers themselves can be judged based on flatness, uniformity, shape, surface cleanliness, edge flatness, and so on.

While these parameters do not sound like much, their use in microelectronics manufacturing necessitates precision at a scale that is hard to comprehend. The tolerance for flatness in advanced substrate manufacturing is below 20nm on a wafer, scaling that up is equivalent to the height of a single bacteria on a tennis court. The particle tolerance translates to a maximum of 10 grains of sand distributed over an area the size of Munich, while impurity is measured in parts per trillion, which is comparable to a single grain of salt in a tank truck.

Figure 3: R&D Spending of Pureplay Wafer Manufacturers (Company Filings)

Manufacturing slices to Siltronic's standards requires high levels of IP and is only getting increasingly difficult as transistor sizes shrink, and wafer specifications become more stringent. This is why chip manufacturers have developed deep relationships with substrate suppliers who tailor more than 50 parameters to the manufacturer's design rule requirements, a process that often starts years prior to commercialization. Siltronic's reputation and track record, which includes being the first supplier to ship 300mm wafers, team of over 400 engineers, 1,800+ pending/active patents, and its continued, significant R&D investment (see Fig. 3), put the company on excellent competitive footing.

Semiconductor Wafer Industry

Figure 4: Global Semiconductor Wafer Silicon Market (SEMI)

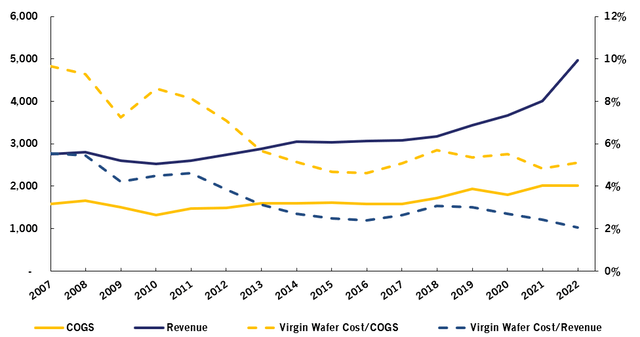

According to industry association SEMI, the global semiconductor silicon market shipped around 14.7bn square inches (>1.300 football pitches) of substrate for USD 13.8bn in 2022 (see Fig. 4). From trough to trough ('09-'19) volumes grew at a CAGR of 5.8%, while revenues compounded at 5.3%. Peak to peak ('07-'22) volumes grew at a 3.6% CAGR, while revenues only compounded at 0.9%. There are two caveats to this data. First it should be mentioned that, after a string of very pronounced boom and bust cycles, the industry decided not to expand capacity without securing significant long-term agreements, which took some time to implement but effectively raised utilisation levels and prices across the cycle. A good example for the increased use of LTAs is Siltronic's FabNext which has around 80% of its capacity under such contracts priced above 2021 ASPs - very profitable given Singapore's lower unit costs. Secondly, it is important to note that what had ultimately caused this shift - the period of declining ASPs over the '07-'15 period (see Fig. 4) - looks a lot worse than it was. Siltronic's cost reduction and productivity improvements during this period (variable costs down >40% 2010-2018, employee productivity up >100%) enabled it to offset some of the top line pressure and positioned it well to benefit from the industry's new found discipline.

Figure 5: Wafer Cost and Cost per Gate at different Processes (Sophie Wilson - Director of IC Design Broadcom)

As the transistors on semiconductors shrink further and further, they inevitably march towards their physical limit, while cost per finished wafer (incl. transistors) increases (see Fig. 5). This is beneficial to substrate producers for several reasons. First of all, as chip manufacturers’ cost and revenue per finished wafer increases, virgin wafers will make up a relatively smaller part of the overall number (see Fig. 6), meaning they become less sensitive to virgin wafer prices. Figure 5 also shows that, since the 28nm process, cost per gate/transistor has been increasing. This development will incentivize chip designers to consider sticking to less dense nodes, which will require more substrate area for the same performance. But there are other reasons why designers may opt to have bigger chips on more advanced nodes as well. Without getting into too much detail, performance/watt for semiconductors scales somewhat logarithmically, meaning incremental returns to power are decreasing at some point so there is a sweet spot. Chip designers, such as Apple with its M1 chips, have recently decided to accept larger form factors to increase efficiency. Furthermore, foundries and designers alike are turning to substrate intensive tight silicon integration and heterogenous compute architectures enabled by chiplets/tiles and 3D stacking techniques (e.g. TSMC's CoW and WoW, or Intel's Foveros…), to further improve performance and reduce power consumption.

Figure 6: TSMC's COGS and Revenue per 300mm Wafer equivalent in USD, and Virgin 300mm Wafer Cost Relative to Them (TSMC and SEMI)

Given these trends and an increasing number of use cases in data centres (e.g. large language and diffusion models), automotive (incl. electric vehicles and ADAS), and industrial, as well as the need to store the ever-increasing amount of data, it is not surprising that the semiconductor market is expected to expand from USD 600bn in 2021 to USD 1-1.3tn in 2030 (Tech Insights, McKinsey & Company, and SEMI estimates). ASML, a key manufacturer of lithography equipment, believes that this translates to a wafer area CAGR of 6.5%, or ca. an incremental 780k wafers/month every year between now and then. For perspective, Siltronic's FabNext, a state-of-the-art facility that costs about EUR 2bn and takes around 3 years to build, can put out around 500k wafers/month, ramping over multiple years. Siltronic itself reckons wafer demand will CAGR at around 6%.

Investment Thesis, Things to Watch, and Modelling Considerations

Investment Thesis

As previously mentioned, wafer manufacturers had decided not to embark on capacity expansion without securing customer orders first. This led to what can be characterized as a stand- off where, from mid to late 2010s, utilization kept rising without significant new capacity announcements. The deadlock culminated in a full-blown shortage in 2021 and 2022, during which major players shared that their capacity was booked out years in advance (Sumco through 2026 for example) and that they expected price increases for at least the next 2 years. The situation has changed a little since then, and the slowdown, worst felt in the memory industry, has led Siltronic to announce that it expects FY2023 sales to be significantly lower (5% not significant, 30% too much; Q1 Guidance: -5% YoY), due in part to short-term shipment deferrals. It is important to note here that Siltronic has stated many times that it is willing to cooperate with customers on LTA shipment deferral, but will not compromise on volume or pricing, and that no customer has asked to renegotiate as “they understand this is unacceptable”.

Table 1: Main Assumptions for Table 2 and Figure 7 (Tachytelic Turtle)

These recent developments, which hit at a time when Siltronic's shares already traded at a discount[1], have led to irrational market pricing. Siltronic currently trades at an LTM EV/EBIT of 4.0, but assuming a more reasonable multiple for FY1 the market is pricing in extreme scenario's (see Table 1 and Fig. 7). Combine this with the fact that the LTA's for FabNext, a facility with cash costs >10% below industry, and below corporate average, will provide the company with a conservatively estimated incremental EBIT of EUR 100m once ramped, and one can see how the shares represent an attractive opportunity.

Figure 7: Market Implied Volume and Price Declines at Different EV/EBIT Multiples, Bands Represent 5% Higher/Lower Unit Costs. Chart also Depicts Industry Data for past Volume Declines (Tachytelic Turtle Estimates, Company and SEMI Data)

Given its strong competitive position, the fundamental trends in the semiconductor industry and the visibility into new capacity coming online (build time of around 3 years), Siltronic's long-term prospects remain positive. Siltronic's dividend yield of ca. 4.4%, which under its current dividend policy should be safe at this level unless EBIT declines below ca. EUR 270m (> -45% from 2022, see Table 2 for reference), may serve to increase the patient investor's Vorfreude.

Table 2: EBIT at Different Revenue Levels (Δ Volumes) and Unit COGS ex. Depreciation Inflation above Mid Assumption of 5%, see Table 1 (Tachytelic Turtle Estimates based on Company Data)

Things to Watch

Short-Term Demand: Depending on the design and nature of the chip, turning virgin wafers into usable microchips can take weeks to months. Given the fact that raw and finished goods inventory accumulate along the supply chain in downswings, substrate manufacturers tend to lag end markets by 1-2 quarters, and upswings are more abrupt. This explains Siltronic's more measured outlook for FY23 which has shell shocked investors and analysts price-in scenarios from a time when LTAs were less than 45% (now >65%) of the company's mix and utilisation levels, going into the downswing, and long-term pricing trends were significantly weaker (impact conceptualized in Fig. 8)[2]. To monitor progress, close attention should be paid to commentary from memory and logic foundries on the demand environment. The mood among these companies seems to be improving already (see Intel’s or Samsung’s Q1 commentary).

Figure 8: Conceptualization of Price Fluctuations under Different Regimes (Tachytelic Turtle)

Industry Capacity: As touched upon above, the substrate manufacturers are likely to see demand grow at a respectable pace over the next decade. While evidence points to industry players having learned their lesson from the past, any investor active in this area should use a “trust but verify” approach to capacity investment decisions. Specifically, demand and supply should be monitored closely, using sources like SEMI, Bloomberg, and company materials along the semiconductor value chain. Disclosures by large wafer manufacturers can be particularly helpful, like Sumco Corporation who publishes their estimates for industry capacity and demand on a quarterly basis. It is worth mentioning here that Siltronic has good visibility into its customers’ investments, remains confident in underlying demand trends, and expects a significant and fast recovery out of the current downturn (4Q 2022 Call).

Competition from China: While the Central Government's semiconductor efforts are more focused on lithography and advanced packaging, Siltronic does not rule out that Chinese manufacturers will compete with the company at some point in the future. However, they are closely monitoring PRC progress and are, and have been in the past, comfortable stating that Chinese alternatives will not pose a threat within the next 5 years. The complexity of semiconductor wafer manufacturing is far exceeding anything used in the solar industry, and many factors play into the dynamic. Node qualifications, for example, built upon one another and leapfrogging a generation is extremely difficult. Chinese players also have difficulty sourcing domestic, semiconductor grade polysilicon, which is five orders of magnitude purer than the solar variant. Further comfort can be taken from the fact that Siltronic obtained a few wafers out of China in Q4 2018 and determined that the performance of Chinese test wafers was "disappointing", and their epi substrate used a technology Siltronic used 12 years ago. Even when compared to old Siltronic wafers, performance of the Chinese epis "was somehow behind".

Modelling Considerations

Foreign Exchange: Siltronic’s revenue skews heavily towards USD (80%), while its costs are EUR heavy (60%). A 1 cent change in the EUR/USD exchange rate would lead to a ca. EUR 13m variation in revenue. In part due to time constraints, I have decided to take guidance at face value, as the company shared that at an average 2023 exchange rate of EUR/USD 1.10 would be “offset by a positive effect from slightly higher prices”. Any proper model should account for exchange rate more explicitly.

FabNext: 80% of FabNext output (ca. 657m square inch when ramped) is on LTAs with ASP per inch estimated above USD 0.90, possibly significantly higher because epi share is high. The company expects to make EBITDA margins exceeding 50% on its product and is ramping at 150k wafers/month (16.4m square inch) every year for ca. 3.3 years.

CapEx: 2023 will see one last step up in CapEx (ca. EUR 1.1-1.2bn) mainly for FabNext expenditures. Siltronic expects to finance this from existing liquidity and cash generated internally. In 2024 CapEx will approximately halve and may head lower thereafter. Historically maintenance CapEx was ca. EUR 80m, with an additional EUR 50-200m for debottlenecking and capability enhancement.

[1]A term used to refer to the 7 companies formerly dominating the polysilicon market.

[2]After a 2021 bid that valued the company at an EV/EBIT of around 18x at the time failed to receive approval from German authorities by the Jan 2022 deadline.

[3] During the 4Q 2022 earnings call management shared that, thus far, pricing is flat QoQ for 1Q 2023, while LTA prices continue to increase.

Disclaimer - This is not investment advice. Do your own due diligence. I make no representation, warranty, or undertaking, express or implied, as to the accuracy, reliability, completeness, or reasonableness of the information contained in this report. Any assumptions, opinions, and estimates expressed in this report constitute my judgment as of the date thereof and are subject to change without notice. Any projections contained in the report are based on a number of assumptions as to market conditions. There is no guarantee that projected outcomes will be achieved. Tachy’s Stack is not acting as your financial advisor or in any fiduciary capacity.

Why has this investment not worked?

Very nice analysis.

How important would labor costs be in the value chain, which would make Chinese competition more attractive on costs? Or is quality and specification more important?